मेरा IC डिज़ाइन करियर 1978 में DRAM डिज़ाइन के साथ शुरू हुआ, इसलिए मैंने डिज़ाइन चुनौतियों, प्रक्रिया अपडेट और नवाचारों को नोट करने के लिए मेमोरी डिज़ाइन के इस क्षेत्र के विकास पर नज़र रखी है। Synopsys की मेजबानी की स्मृति प्रौद्योगिकी संगोष्ठी नवंबर 2022 में, और मुझे एसके हाइनिक्स इंजीनियरों, ताए-जून ली और बोंग-गिल कांग की एक प्रस्तुति देखने का मौका मिला। DRAM चिप्स हाल ही की तरह 9.6 गीगाबिट्स प्रति सेकंड की उच्च क्षमता और तेज़ डेटा दरों तक पहुँच गए हैं एलपीडीडीडीआर5टी 25 जनवरी को घोषणा पावर डिलीवरी नेटवर्क (पीडीएन) की अखंडता द्वारा डेटा दरों को सीमित किया जा सकता है, फिर भी पीडीएन के साथ एक पूर्ण-चिप डीआरएएम का विश्लेषण करने से सिमुलेशन समय बहुत धीमा हो जाएगा।

पीक मेमोरी बैंडविड्थ प्रति x64 चैनल ने कई पीढ़ियों में स्थिर वृद्धि दिखाई है:

- DDR1, 3.2GB/s 2.5V आपूर्ति पर

- DDR2, 6.4GB/s 1.8V आपूर्ति पर

- DDR3, 12.8GB/s 1.5V आपूर्ति पर

- DDR4, 25.6GB/s 1.2V आपूर्ति पर

- DDR5, 51.2GB/s 1.1V आपूर्ति पर

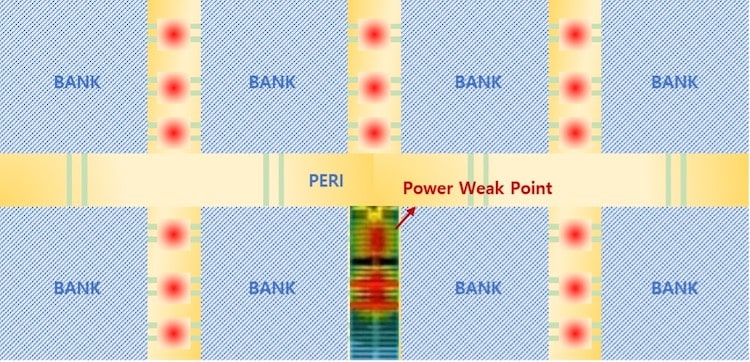

इन आक्रामक समय लक्ष्यों को पूरा करने में एक बड़ी चुनौती डीआरएएम सरणी के आईसी लेआउट के दौरान परजीवी आईआर ड्रॉप मुद्दों को नियंत्रित करना है, और नीचे दिखाया गया आईआर ड्रॉप का एक प्लॉट है जहां लाल रंग उच्चतम वोल्टेज ड्रॉप का क्षेत्र है, जो बदले में स्मृति के प्रदर्शन को धीमा कर देता है।

एक IC के लिए निकाले गए परजीवी एक SPF फ़ाइल प्रारूप में सहेजे जाते हैं, और इन परजीवी को PDN के लिए SPICE नेटलिस्ट में जोड़ने से सर्किट सिम्युलेटर 64X के कारक से धीमा हो जाता है, जबकि PDN द्वारा जोड़े गए परजीवी RC तत्वों की संख्या है केवल सिग्नल परजीवी से 3.7 गुना अधिक।

SK hynix में, उन्होंने प्राइमसिम™ प्रो तीन तकनीकों का उपयोग करके पीडीएन सहित एसपीएफ़ नेटलिस्ट्स पर सर्किट सिम्युलेटर:

- पावर और अन्य सिग्नल के बीच नेटलिस्ट का विभाजन

- पीडीएन में आरसी तत्वों में कमी

- सिमुलेशन घटना सहिष्णुता को नियंत्रित करना

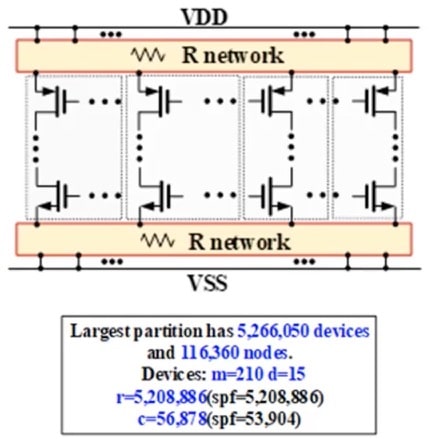

प्राइमसिम प्रो कनेक्टिविटी के आधार पर नेटलिस्ट को विभाजित करने के लिए विभाजन का उपयोग करता है, और डिफ़ॉल्ट रूप से पीडीएन और अन्य सिग्नल बहुत बड़े विभाजन बनाने के लिए गठबंधन करेंगे, जो बदले में सिमुलेशन समय को बहुत धीमा कर देते हैं। यहाँ डिफ़ॉल्ट सिम्युलेटर सेटिंग्स के साथ सबसे बड़ा विभाजन कैसा दिखता है:

प्राइमसिम प्रो में एक विकल्प (primesim_pwrblock) का उपयोग पीडीएन को अन्य संकेतों से अलग करते हुए, सबसे बड़े विभाजन के आकार में कटौती करने के लिए किया गया था।

एसपीएफ़ प्रारूप में निकाले गए पीडीएन में बहुत अधिक आरसी तत्व थे, जो सर्किट सिमुलेशन रन टाइम को धीमा कर देते थे, इसलिए एक विकल्प कहा जाता था primesim_postl_rcred एक ही समय में सटीकता को संरक्षित करते हुए आरसी नेटवर्क को कम करने के लिए उपयोग किया गया था। आरसी कटौती विकल्प आरसी तत्वों की संख्या को 73.9% तक कम करने में सक्षम था।

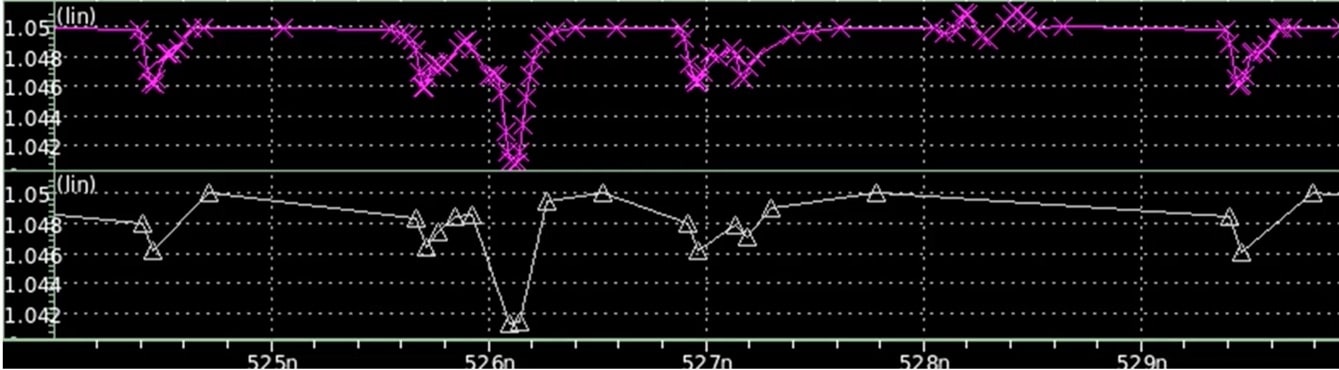

प्राइमसिम प्रो जैसे सर्किट सिमुलेटर नेटलिस्ट विभाजन में करंट और वोल्टेज को हल करने के लिए मैट्रिक्स गणित का उपयोग करते हैं, इसलिए रनटाइम सीधे मैट्रिक्स आकार से संबंधित होता है और कितनी बार वोल्टेज परिवर्तन के लिए पुनर्गणना की आवश्यकता होती है। सिम्युलेटर विकल्प primesim_evtgrid_for_pdn का उपयोग किया गया था, और यह पीडीएन में छोटे वोल्टेज परिवर्तन होने पर मैट्रिक्स को हल करने की संख्या को कम करता है। बैंगनी रंग में दिखाए गए नीचे दिए गए चार्ट में उस समय प्रत्येक बिंदु पर एक एक्स होता है जब पीडीएन में मैट्रिक्स को हल करना डिफ़ॉल्ट रूप से आवश्यक होता है, फिर सफेद रंग में दिखाए गए प्रत्येक बिंदु पर त्रिभुज होते हैं जब सिम्युलेटर विकल्प के साथ मैट्रिक्स सॉल्विंग का उपयोग किया जाता है। बैंगनी एक्स की तुलना में सफेद त्रिकोण बहुत कम बार होते हैं, जिससे तेज सिमुलेशन गति को सक्षम किया जाता है।

रनटाइम को कम करने के लिए उपयोग किया जाने वाला अंतिम फाइनसिम प्रो सिम्युलेटर विकल्प था primesim_pdn_event_control= ए: बी, और यह ए: बी के लिए एक आदर्श शक्ति स्रोत लागू करके काम करता है, जिसके परिणामस्वरूप पीडीएन के लिए कम मैट्रिक्स गणना होती है।

सभी फाइनसिम प्रो विकल्पों का संयुक्त उपयोग करके सिमुलेशन रनटाइम सुधार 5.2X स्पीड-अप था।

सारांश

SK हाइनिक्स के इंजीनियर अपने मेमोरी चिप डिजाइनों में विश्लेषण के लिए फाइनसिम और प्राइमसिम सर्किट सिमुलेटर दोनों का उपयोग कर रहे हैं। प्राइमसिम प्रो में चार विकल्पों का उपयोग करने से एसपीएफ़ पैरासिटिक्स के साथ पूर्ण-चिप पीडीएन विश्लेषण की अनुमति देने के लिए पर्याप्त गति सुधार प्रदान किया गया है। मुझे उम्मीद है कि मेमोरी चिप और अन्य आईसी डिजाइन शैलियों की बढ़ती चुनौतियों का सामना करने के लिए Synopsys अपने सर्किट सिम्युलेटर परिवार में नवाचार करना और सुधार करना जारी रखेगा।

संबंधित ब्लॉग

इस पोस्ट को इसके माध्यम से साझा करें:

- एसईओ संचालित सामग्री और पीआर वितरण। आज ही प्रवर्धित हो जाओ।

- प्लेटोब्लॉकचैन। Web3 मेटावर्स इंटेलिजेंस। ज्ञान प्रवर्धित। यहां पहुंचें।

- स्रोत: https://semiwiki.com/eda/324168-power-delivery-network-analysis-in-dram-design/