IC-tervezői pályafutásom a DRAM-tervezéssel kezdődött még 1978-ban, így folyamatosan figyelemmel kísértem a memóriatervezés ezen területére vonatkozó fejleményeket, hogy felfigyeljek a tervezési kihívásokra, a folyamatfrissítésekre és az újításokra. A Synopsys házigazdája a memóriatechnológiai szimpózium 2022 novemberében volt lehetőségem megnézni az SK hynix mérnökei, Tae-Jun Lee és Bong-Gil Kang előadását. A DRAM chipek nagy kapacitást és gyors, 9.6 gigabit/s adatátviteli sebességet értek el, mint a legutóbbi LPDDDR5T január 25-i bejelentés. Az adatátviteli sebességet korlátozhatja a Power Delivery Network (PDN) integritása, de a teljes chipes DRAM PDN-nel történő elemzése túlságosan lelassítja a szimulációs időt.

Az x64-es csatornánkénti maximális memóriasávszélesség folyamatos növekedést mutat több generáción keresztül:

- DDR1, 3.2 GB/s 2.5 V-os tápellátással

- DDR2, 6.4 GB/s 1.8 V-os tápellátással

- DDR3, 12.8 GB/s 1.5 V-os tápellátással

- DDR4, 25.6 GB/s 1.2 V-os tápellátással

- DDR5, 51.2 GB/s 1.1 V-os tápellátással

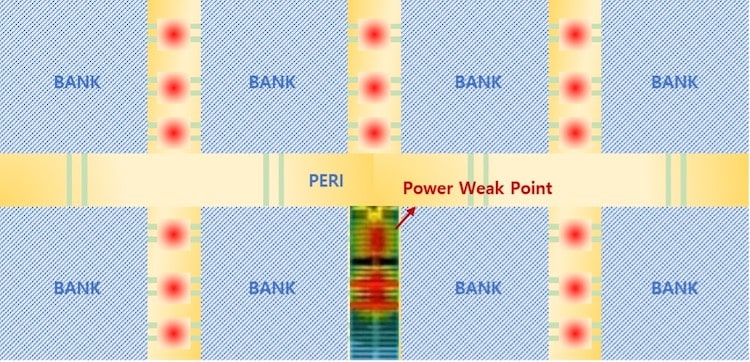

Ezen agresszív időzítési célok teljesítésében nagy kihívást jelent a DRAM tömb IC-elrendezése során fellépő parazita infravörös leesési problémák szabályozása. Az alábbiakban az IR-esés diagramja látható, ahol a piros szín a legnagyobb feszültségeséssel járó terület. lelassítja a memória teljesítményét.

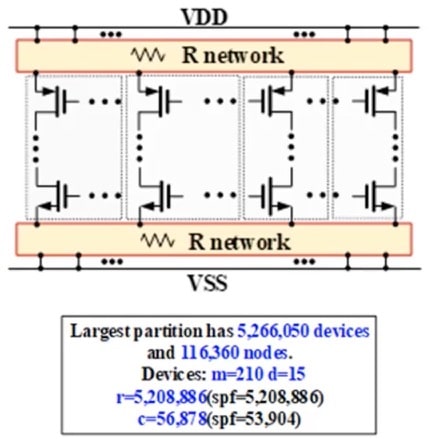

Az IC-ből kivont paraziták SPF fájlformátumban kerülnek mentésre, és ha ezeket a PDN-hez tartozó parazitákat hozzáadjuk a SPICE hálózatlistához, az áramkör-szimulátor 64-szeresére lassul, míg a PDN által hozzáadott parazita RC elemek száma 3.7X több, mint pusztán jelparaziták.

Az SK hynixnél egy pragmatikus megközelítést dolgoztak ki a szimuláció futási idejének csökkentésére a PrimeSim™ Pro áramkör-szimulátor SPF-hálózati listákon, beleértve a PDN-t is, három technikával:

- A hálózati lista felosztása a teljesítmény és más jelek között

- Az RC-elemek csökkentése a PDN-ben

- Szimulációs eseménytűrés szabályozása

A PrimeSim Pro particionálást használ a hálózati lista felosztására a kapcsolat alapján, és alapértelmezés szerint a PDN és más jelek együttesen nagyon nagy partíciókat alkotnak, ami viszont túlságosan lelassította a szimulációt. Így nézett ki a legnagyobb partíció a szimulátor alapértelmezett beállításaival:

Egy lehetőség a PrimeSim Pro-ban (Primesim_pwrblock) segítségével csökkentették a legnagyobb partíció méretét, elválasztva a PDN-t a többi jeltől.

Az SPF formátumban kinyert PDN túl sok RC elemet tartalmazott, ami lelassította az áramkör szimuláció futási idejét, ezért egy opció ún. Primesim_postl_rcred Az RC hálózat csökkentésére használták, ugyanakkor megőrizték a pontosságot. Az RC-csökkentési lehetőség akár 73.9%-kal is csökkentette az RC-elemek számát.

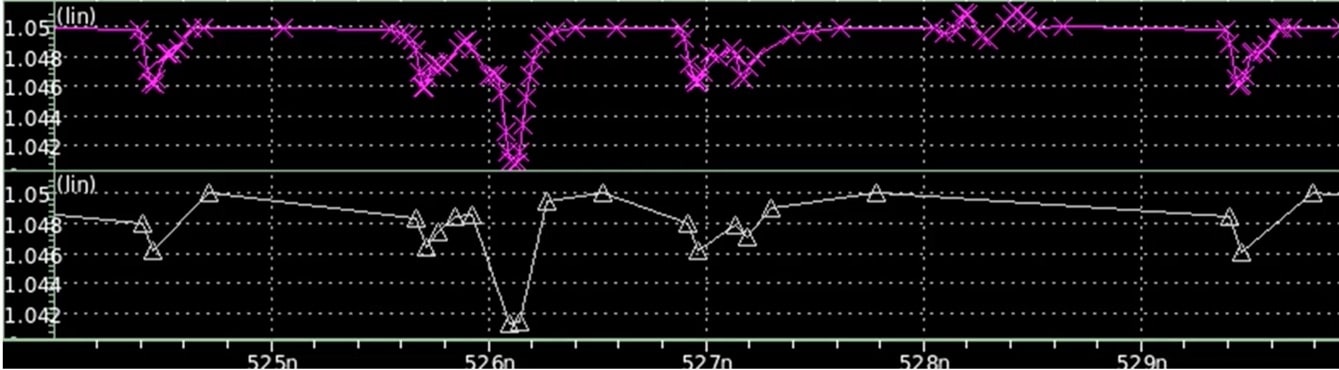

Az áramkör-szimulátorok, mint például a PrimSim Pro, mátrix matematikai megoldásokat használnak a hálózatlista partícióiban lévő áram és feszültség meghatározására, így a futásidő közvetlenül kapcsolódik a mátrix méretéhez, és ahhoz, hogy a feszültségváltozás milyen gyakran igényel újraszámítást. A szimulátor opció primesim_evtgrid_for_pdn használták, és csökkenti a mátrix megoldásának számát, amikor kis feszültségváltozások vannak a PDN-ben. Az alábbi, lilával ábrázolt diagramon X van minden olyan időpontban, amikor a PDN-ben alapértelmezés szerint mátrixmegoldásra volt szükség, majd fehér színnel háromszögek láthatók minden olyan időpontban, amikor a mátrixmegoldást a szimulátor opcióval használják. A fehér háromszögek sokkal ritkábban fordulnak elő, mint a lila X-ek, ami nagyobb szimulációs sebességet tesz lehetővé.

Az utolsó FineSim Pro szimulátor opció a futási idő csökkentésére volt primesim_pdn_event_control=a:b, és úgy működik, hogy ideális áramforrást alkalmaz a:b-hez, ami kevesebb mátrixszámítást eredményez a PDN számára.

A FineSim Pro összes opciójának felhasználásával végzett szimulációs futásidejű fejlesztések 5.2-szeres gyorsulást eredményeztek.

Összegzésként

Az SK hynix mérnökei a FineSim és a PrimeSim áramköri szimulátorokat is felhasználták memóriachip-terveik elemzéséhez. A PrimeSim Pro négy opciójának használata elegendő sebességnövekedést eredményezett ahhoz, hogy lehetővé tegye a teljes chipes PDN elemzést az SPF parazitákkal együtt. Arra számítok, hogy a Synopsys folytatja az áramkör-szimulátor-család innovációját és fejlesztését, hogy megfeleljen a memóriachipek és más IC-tervezési stílusok növekvő kihívásainak.

Kapcsolódó blogok

Oszd meg ezt a bejegyzést ezen keresztül:

- SEO által támogatott tartalom és PR terjesztés. Erősödjön még ma.

- Platoblockchain. Web3 metaverzum intelligencia. Felerősített tudás. Hozzáférés itt.

- Forrás: https://semiwiki.com/eda/324168-power-delivery-network-analysis-in-dram-design/