テクノロジーとしてのチップレットの出現は、半導体業界の変曲点です。 電子システムの実装にチップレットベースのアプローチを採用することの潜在的な利点については議論の余地がありません。 より小型の事前製造されたコンポーネントであるチップレットを組み合わせてより大きなシステムを作成することができ、モノリシック集積回路と比較して柔軟性、スケーラビリティ、および費用対効果の向上などの利点を提供します。 ただし、チップレットは、設計、統合、およびテストの面で新しい課題も提示します。 この技術はまだ流動的であり、今後数年間で対処する必要がある多くの不明な点があります。 チップレットの成功は、製造能力、設計の専門知識、チップレットを既存のシステムに統合する能力などの要因に依存します。

洗練されたパッケージングと相互接続技術は多くの報道を受けていますが、重要な側面は他にもたくさんあります。 チップレットベースのシステムを設計するには、従来のチップ設計とは異なる考え方とスキルセットが必要です。 チップレットベースの経済を実現するには、さらに多くのものを組み合わせる必要があります。 これは、最近開催された「The Rise of the Chiplet」というウェビナーの焦点でした。 このウェビナーは、SemiEngineering.com の技術編集者/EDA である Brian Bailey によってモデレートされました。 パネリストは、Achronix の製品計画担当シニア ディレクターである Nick Ilyadis でした。 Rich Wawrzyniak 氏、主席アナリスト ASIC & SoC、Semico Research Corp; Open Compute Project Foundation の OCP ODSA プロジェクト リードである Bapi Vinnakota 氏。

パネルの構成により、聴衆は市場の視点、製品の視点、および効率をソリューションに設計するための共同コミュニティの視点を聞くことができました。

チップレット採用に必要なもの

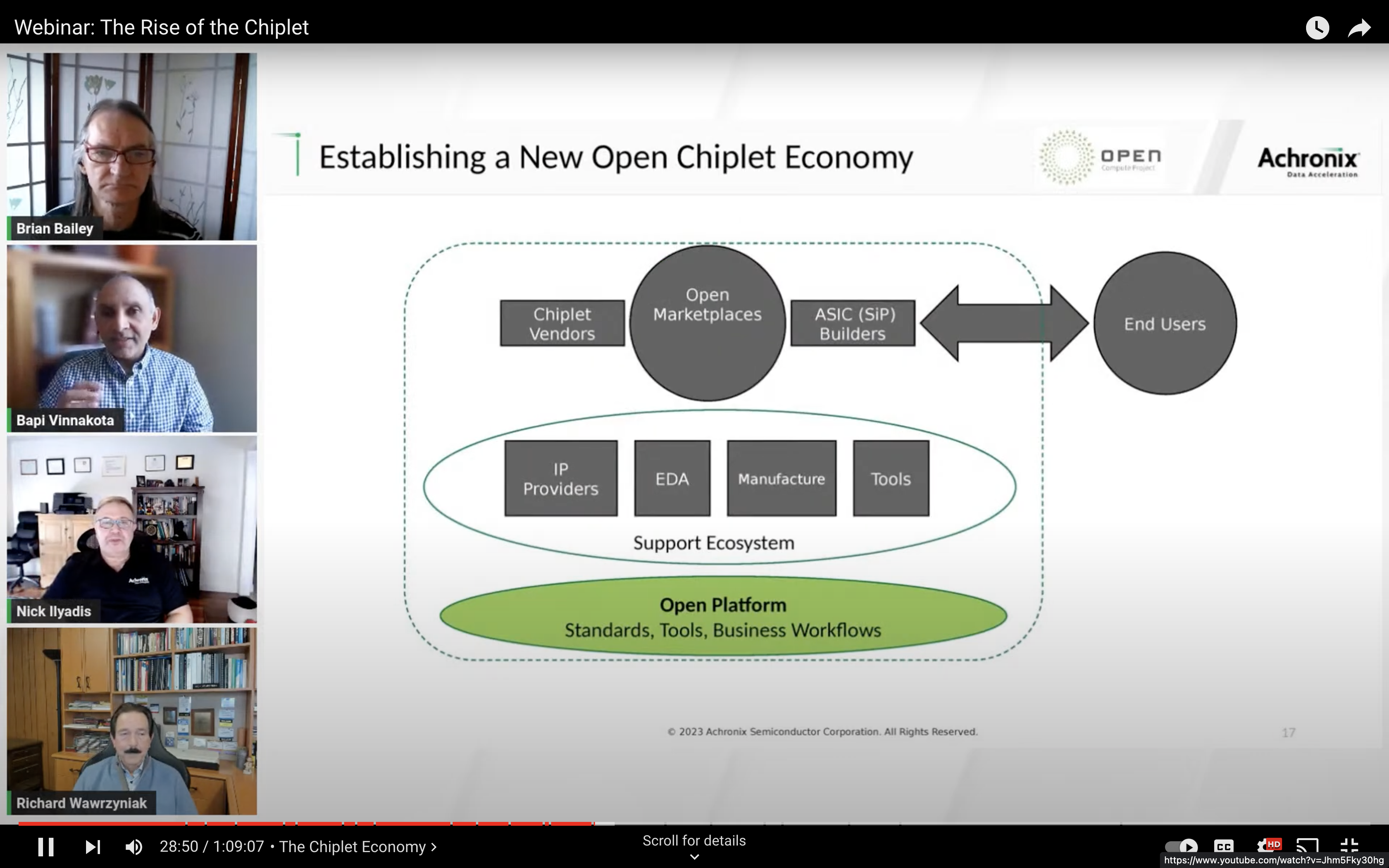

チップレットの採用に関して、業界はダイ間インターフェースとパッケージング技術だけでなく、チップレットの経済全体について心配する必要があります。

たとえば、効率的なモジュール性を実現するために、チップレットをビルドする前にどのように記述するか。 チップレットの物理的な説明に含める標準的なものは、面積、方向、サーマル マップ、電力供給、バンプ マップなどです。この物理的なパーツの説明は、複数のベンダーのチップレットを統合する場合に非常に重要です。 OCP は JEDEC と協力して、チップレットを物理的に記述する標準 JEP30 パーツ モデルの作成を開始しています。 対処すべきその他の分野には次のようなものがあります。 アーキテクチャの探索をどのように達成するか? ビジネスロジスティクスをどのように処理しますか?

OCP 内のさまざまなワークグループは、これらの分野の多くに焦点を当てており、デザイナーが使用できるダウンロード可能なワークシートまたはテンプレートを利用できるようにしています。 たとえば、設計者はワークシートをダウンロードして、チップレット ベースの設計とモノリシック設計の設計コストと製造コストを比較できます。 チップレット インターフェイスに関しては、たとえば、一部のアプリケーションでは Bunch of Wires (BoW) が選択され、他の一部のアプリケーションでは Universal Chiplet Interconnect Express (UCIe) が適切な選択肢になる場合があります。 市場で入手可能なさまざまなダイ間インターフェースを比較するためのツールが用意されています。

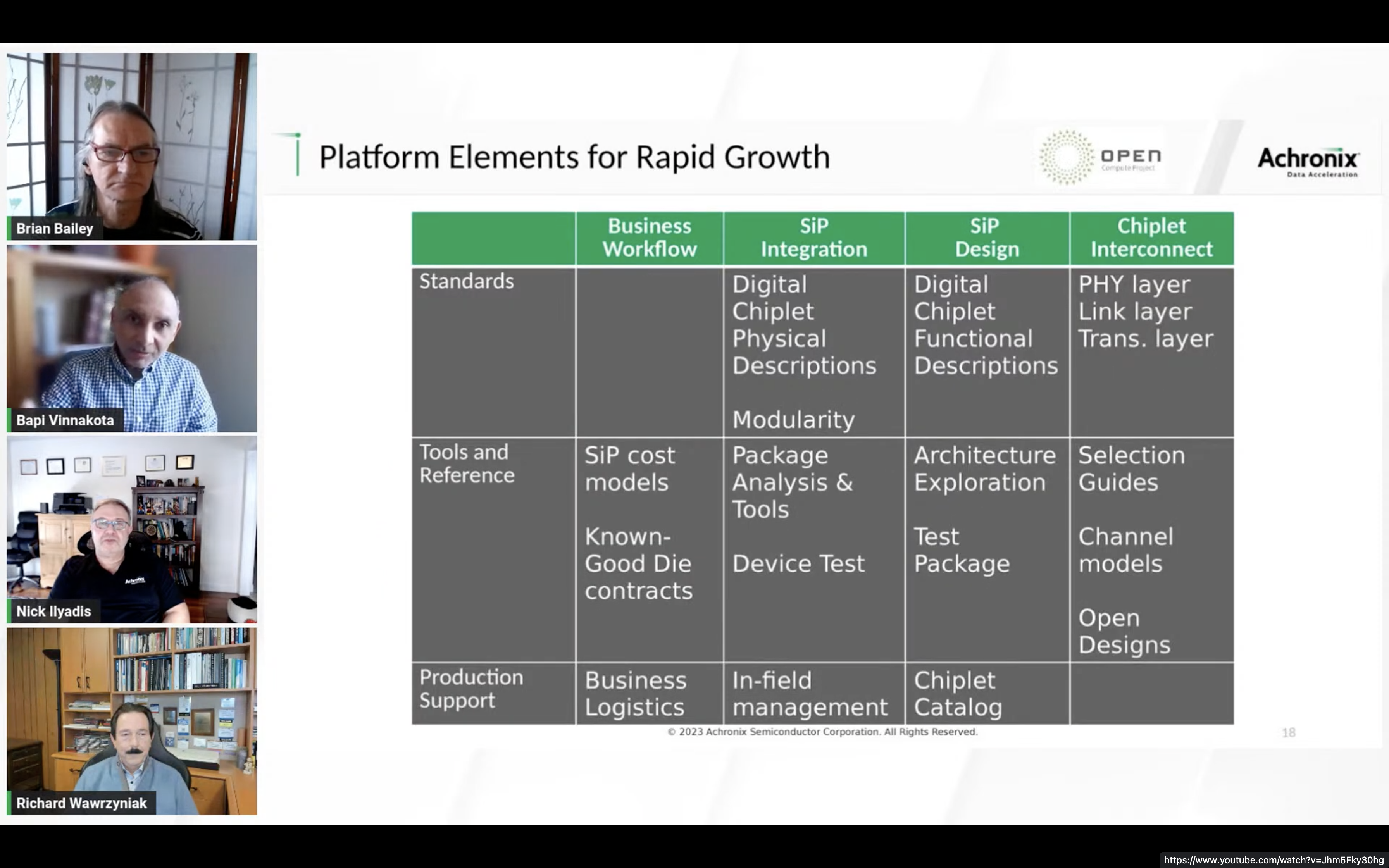

次の表は、対処する必要があるさまざまな領域を示しています。

理解し対処する必要があるもう XNUMX つの重要なことは、製品に含まれるすべてのチップレットが同じプロセス コーナーからのものである必要があるかどうかです。 チップレットは、メモリのように異なるスピード グレードで販売する必要がありますか? 一部のチップレットが高速コーナーからのもので、他のチップレットが低速コーナーからのものである場合、システム シミュレーション中およびフィールドでの展開時にどのような問題が発生しますか?

チップレット技術が進化し続けるにつれて、企業はチップレットを製品に組み込むためのさまざまなアプローチを試しています。

eFPGAベースのチップレット

組み込み FPGA (eFPGA) は、モノリシック ASIC の世界で大きな注目を集めています。 eFPGA ベースのチップレットは、eFPGA の利点を完全なチップレット ベースのシステムに拡張できます。 FPGA ソリューション スペースのリーダーとしての Achronix は、eFPGA IP ベースのチップレットを提供して、次の利点を提供します。 独自の生産ソリューション (異なる SKU); ASIC に最適なプロセス テクノロジが組み込み FPGA に最適でない場合に、さまざまなプロセス テクノロジをサポートします。 FPGA チップレットを XNUMX つのモノリシック デバイスで使用するのではなく、複数世代の製品で使用できます。

まとめ

チップレットは、半導体産業に有望な新しい方向性を提供します。 勝者のソリューションは、今後数年間で決定されます。 何年、それはあなたが尋ねる人に依存します。 ウェビナー全体を聞くには、ここをクリックしてください。 パネリストは、あなたが興味を持っているかもしれない多くの聴衆の質問にも答えました.

また読む:

エッジでの AI のプラットフォーム選択に関する Achronix

この投稿を共有する:

- SEO を活用したコンテンツと PR 配信。 今日増幅されます。

- Platoblockchain。 Web3メタバースインテリジェンス。 知識の増幅。 こちらからアクセスしてください。

- 情報源: https://semiwiki.com/chiplet/326537-the-rise-of-the-chiplet/