Min IC-designkarriere startet med DRAM-design tilbake i 1978, så jeg har fulgt med på utviklingen innen dette området av minnedesign for å legge merke til designutfordringene, prosessoppdateringer og innovasjoner underveis. Synopsys var vert for en minneteknologi symposium i november 2022, og jeg hadde en sjanse til å se en presentasjon fra SK hynix-ingeniører, Tae-Jun Lee og Bong-Gil Kang. DRAM-brikker har nådd høy kapasitet og raske datahastigheter på 9.6 gigabit per sekund, som den siste LPDDDR5T kunngjøring 25. januar. Datahastigheter kan begrenses av integriteten til Power Delivery Network (PDN), men å analysere en full-chip DRAM med PDN vil redusere simuleringstidene for mye.

Den maksimale minnebåndbredden per x64-kanaler har vist jevn vekst over flere generasjoner:

- DDR1, 3.2 GB/s ved 2.5V forsyning

- DDR2, 6.4 GB/s ved 1.8V forsyning

- DDR3, 12.8 GB/s ved 1.5V forsyning

- DDR4, 25.6 GB/s ved 1.2V forsyning

- DDR5, 51.2 GB/s ved 1.1V forsyning

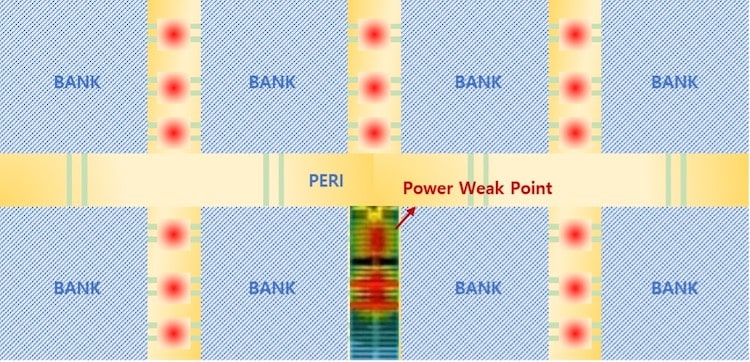

En stor utfordring med å møte disse aggressive timingmålene er å kontrollere de parasittiske IR-fallproblemene forårsaket under IC-oppsettet til DRAM-arrayen, og vist nedenfor er et plott av IR-fall der den røde fargen er et område med høyeste spenningsfall, som igjen reduserer ytelsen til minnet.

De ekstraherte parasittene for en IC lagres i et SPF-filformat, og å legge til disse parasittene for PDN til en SPICE-nettliste får kretssimulatoren til å bremse ned med en faktor på 64X, mens antallet parasittiske RC-elementer lagt til av PDN er 3.7 ganger mer enn bare signalparasitter.

Hos SK hynix kom de opp med en pragmatisk tilnærming for å redusere simuleringskjøringstidene ved bruk av PrimeSim™ Pro kretssimulator på SPF-nettlister inkludert PDN ved å bruke tre teknikker:

- Partisjonering av nettlisten mellom strøm og andre signaler

- Reduksjon av RC-elementer i PDN

- Kontrollere simuleringshendelsestoleranse

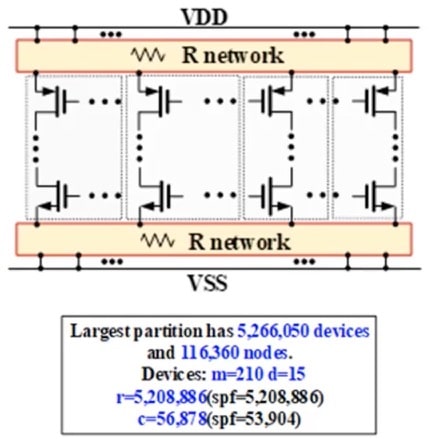

PrimeSim Pro bruker partisjonering for å dele opp nettlisten basert på tilkobling, og som standard vil PDN og andre signaler kombineres for å danne veldig store partisjoner, som igjen bremset simuleringstidene for mye. Her er hvordan den største partisjonen så ut med standard simulatorinnstillinger:

Et alternativ i PrimeSim Pro (primesim_pwrblock) ble brukt til å kutte ned størrelsen på den største partisjonen, og skille PDN fra andre signaler.

Den utpakkede PDN-en i SPF-format hadde for mange RC-elementer, noe som reduserte kjøretidene for kretssimulering, så et alternativ kalt primesim_postl_rcred ble brukt til å redusere RC-nettverket, samtidig som nøyaktigheten ble bevart. Alternativet for RC-reduksjon var i stand til å redusere antall RC-elementer med opptil 73.9 %.

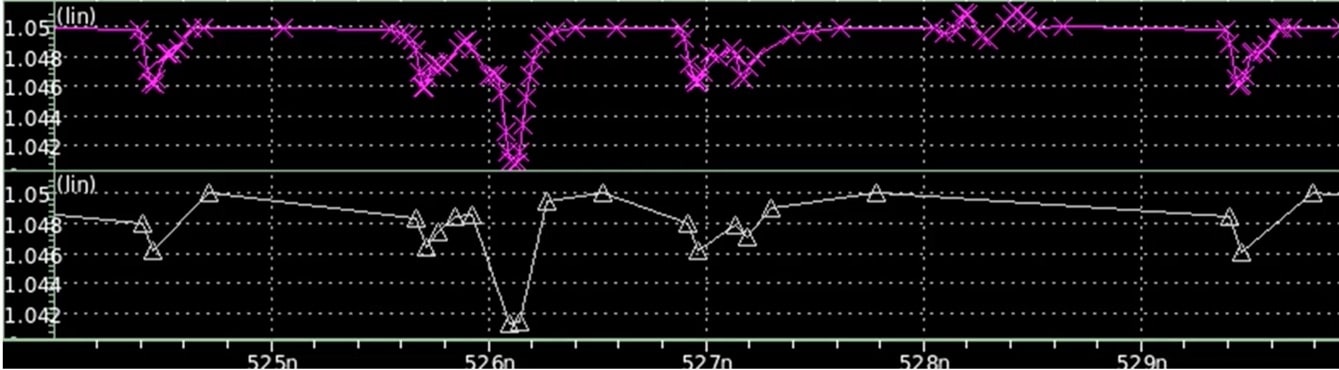

Kretssimulatorer som PrimSim Pro bruker matrisematematikk for å løse for strøm og spenninger i nettlistepartisjonene, så kjøretiden er direkte relatert til matrisestørrelsen og hvor ofte en spenningsendring krever omberegning. Simulatoralternativet primesim_evtgrid_for_pdn ble brukt, og det reduserer antall ganger en matrise må løses når det er små spenningsendringer i PDN. Diagrammet nedenfor vist i lilla har en X på hvert tidspunkt da matriseløsning i PDN var påkrevd som standard, og deretter vist i hvitt er trekanter på hvert tidspunkt matriseløsning brukes med simulatoralternativet. De hvite trekantene skjer mye sjeldnere enn de lilla X-ene, noe som muliggjør raskere simuleringshastigheter.

Et siste FineSim Pro-simulatoralternativ som ble brukt for å redusere kjøretidene var primesim_pdn_event_control=a:b, og det fungerer ved å bruke en ideell strømkilde for a:b, noe som resulterer i færre matriseberegninger for PDN.

Simuleringen av kjøretidsforbedringene ved å bruke alle FineSim Pro-alternativene kombinert var en 5.2X-hastighet.

Oppsummering

Ingeniører ved SK hynix har brukt både FineSim- og PrimeSim-kretssimulatorene for analyse i deres minnebrikkedesign. Bruk av fire alternativer i PrimeSim Pro har gitt tilstrekkelige hastighetsforbedringer til å tillate full-chip PDN-analyse med SPF-parasitter inkludert. Jeg forventer at Synopsys vil fortsette å innovere og forbedre sin kretssimulatorfamilie for å møte de økende utfordringene med minnebrikke og andre IC-designstiler.

Relaterte blogger

Del dette innlegget via:

- SEO-drevet innhold og PR-distribusjon. Bli forsterket i dag.

- Platoblokkkjede. Web3 Metaverse Intelligence. Kunnskap forsterket. Tilgang her.

- kilde: https://semiwiki.com/eda/324168-power-delivery-network-analysis-in-dram-design/