Moja kariera pri oblikovanju IC se je začela z oblikovanjem DRAM-a leta 1978, zato sem spremljal razvoj na tem področju oblikovanja pomnilnika, da bi opazil izzive pri načrtovanju, posodobitve postopkov in inovacije na poti. Synopsys je gostil a simpozij pomnilniške tehnologije novembra 2022 in imel sem priložnost gledati predstavitev inženirjev SK hynix, Tae-Jun Leeja in Bong-Gil Kanga. Čipi DRAM so dosegli visoko zmogljivost in hitre podatkovne hitrosti 9.6 gigabitov na sekundo, kot nedavni LPDDDR5T objava 25. januarja. Hitrost prenosa podatkov je lahko omejena s celovitostjo omrežja za dostavo električne energije (PDN), vendar bo analiza DRAM-a s polnim čipom s PDN preveč upočasnila čas simulacije.

Najvišja pasovna širina pomnilnika na kanale x64 je pokazala stalno rast v več generacijah:

- DDR1, 3.2 GB/s pri 2.5 V napajanju

- DDR2, 6.4 GB/s pri 1.8 V napajanju

- DDR3, 12.8 GB/s pri 1.5 V napajanju

- DDR4, 25.6 GB/s pri 1.2 V napajanju

- DDR5, 51.2 GB/s pri 1.1 V napajanju

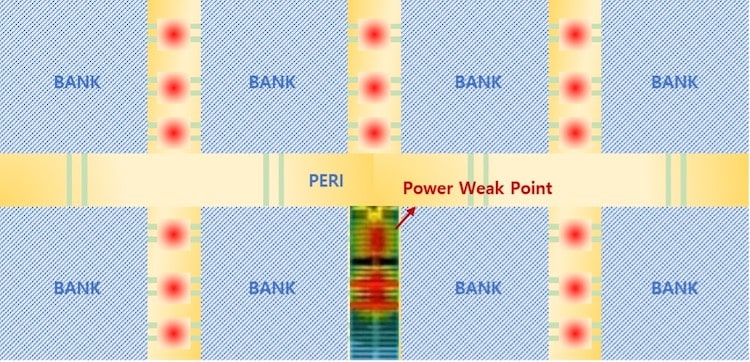

Velik izziv pri izpolnjevanju teh agresivnih časovnih ciljev je nadzor nad parazitskimi težavami padca IR, ki nastanejo med postavitvijo IC niza DRAM, spodaj pa je prikazan graf padca IR, kjer je rdeča barva območje največjega padca napetosti, kar pa upočasni delovanje pomnilnika.

Ekstrahirani paraziti za IC so shranjeni v formatu datoteke SPF in dodajanje teh parazitov za PDN na SPICE netlist povzroči, da se simulator vezja upočasni za faktor 64X, medtem ko je število parazitskih elementov RC, ki jih doda PDN, 3.7-krat več kot le paraziti signala.

Pri SK hynix so se domislili pragmatičnega pristopa za zmanjšanje časa izvajanja simulacije pri uporabi PrimeSim™ Pro simulator vezja na seznamih omrežij SPF, vključno s PDN, z uporabo treh tehnik:

- Razdelitev seznama omrežij med Power in drugimi signali

- Zmanjšanje RK elementov v PDN

- Nadzor tolerance simulacijskih dogodkov

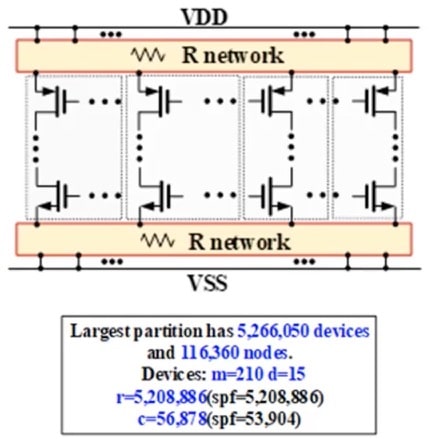

PrimeSim Pro uporablja particioniranje za razdelitev seznama omrežij na podlagi povezljivosti, privzeto pa bi se PDN in drugi signali združili v zelo velike particije, kar je posledično preveč upočasnilo čas simulacije. Tukaj je videti največja particija s privzetimi nastavitvami simulatorja:

Možnost v PrimeSim Pro (primesim_pwrblock) je bil uporabljen za zmanjšanje velikosti največje particije in ločevanje PDN od drugih signalov.

Ekstrahirani PDN v formatu SPF je imel preveč elementov RC, kar je upočasnilo čas izvajanja simulacije vezja, zato je bila uporabljena možnost, imenovana primesim_postl_rcred je bil uporabljen za zmanjšanje RC omrežja, hkrati pa je ohranil natančnost. Možnost zmanjšanja RC je zmanjšala število RC elementov do 73.9 %.

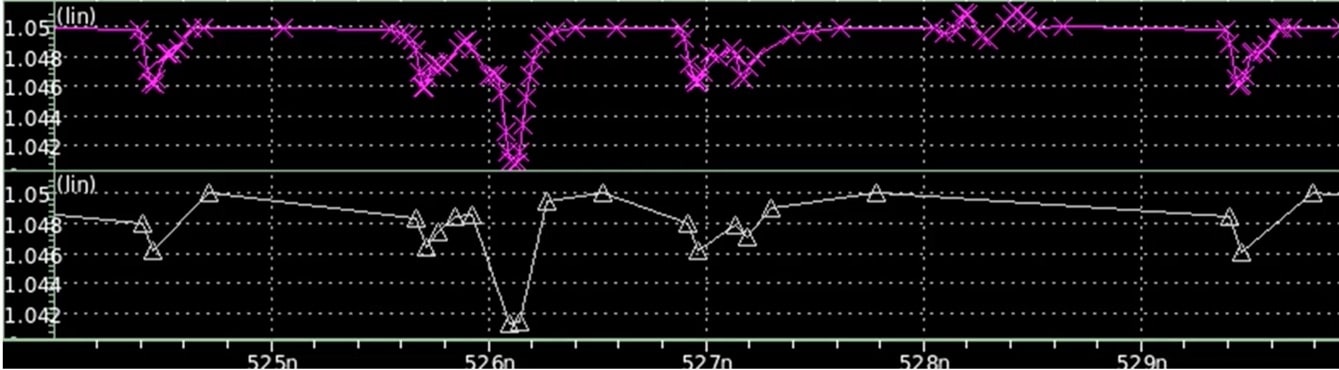

Simulatorji vezij, kot je PrimSim Pro, uporabljajo matrično matematiko za reševanje toka in napetosti v particijah seznama omrežij, zato je čas delovanja neposredno povezan z velikostjo matrike in kako pogosto sprememba napetosti zahteva ponoven izračun. Možnost simulatorja primesim_evtgrid_for_pdn in zmanjša število krat, ko je treba rešiti matriko, kadar koli pride do majhnih sprememb napetosti v PDN. Spodnja tabela, prikazana v vijolični barvi, ima X na vsaki točki v času, ko je bilo privzeto zahtevano reševanje matrike v PDN, nato pa so v beli barvi prikazani trikotniki na vsaki točki v času, ko je reševanje matrike uporabljeno z možnostjo simulatorja. Beli trikotniki se pojavljajo veliko manj pogosto kot vijolični X-ji, kar omogoča večje hitrosti simulacije.

Končna možnost simulatorja FineSim Pro, uporabljena za skrajšanje časa izvajanja, je bila primesim_pdn_event_control=a:b in deluje z uporabo idealnega vira energije za a:b, kar ima za posledico manj matričnih izračunov za PDN.

Izboljšave izvajalnega časa simulacije z uporabo vseh možnosti FineSim Pro skupaj so pomenile 5.2-kratno pospešitev.

Povzetek

Inženirji v podjetju SK hynix uporabljajo simulatorja vezij FineSim in PrimeSim za analizo pri načrtovanju svojih pomnilniških čipov. Uporaba štirih možnosti v PrimeSim Pro je zagotovila zadostne izboljšave hitrosti, ki omogočajo analizo PDN celotnega čipa z vključenimi paraziti SPF. Pričakujem, da bo Synopsys še naprej uvajal inovacije in izboljševal svojo družino simulatorjev vezij, da bi se spopadel z naraščajočimi izzivi pomnilniških čipov in drugih slogov oblikovanja IC.

Sorodni dnevniki

Delite to objavo prek:

- Distribucija vsebine in PR s pomočjo SEO. Okrepite se še danes.

- Platoblockchain. Web3 Metaverse Intelligence. Razširjeno znanje. Dostopite tukaj.

- vir: https://semiwiki.com/eda/324168-power-delivery-network-analysis-in-dram-design/